Tekninen dokumentti

Tekniset tiedot

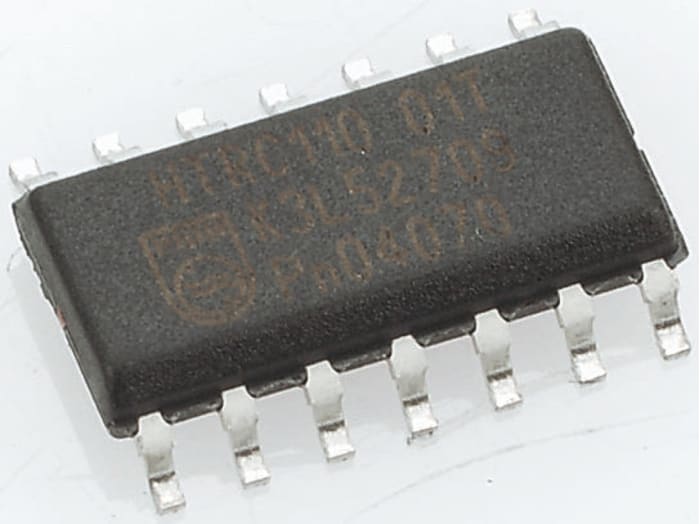

Merkki

NexperiaLogic Family

HC

Logic Function

D Type

Input Type

Single Ended

Output Signal Type

Differential

Triggering Type

Positive Edge

Polarity

Inverting, Non-Inverting

Mounting Type

Surface Mount

Package Type

SOIC

Pin Count

16

Set/Reset

Master Reset

Number of Elements per Chip

4

Maximum Propagation Delay Time @ Maximum CL

175 ns @ 2 V

Maximum Operating Supply Voltage

6 V

Dimensions

10 x 4 x 1.45mm

Height

1.45mm

Width

4mm

Minimum Operating Temperature

-40 °C

Minimum Operating Supply Voltage

2 V

Maximum Operating Temperature

+125 °C

Propagation Delay Test Condition

50pF

Length

10mm

Alkuperämaa

Thailand

Tuotetiedot

74HC Family Flip-Flops & Latches, Nexperia

A range of NXP Flip-Flops and Latches from the 74HC Family of CMOS Logic ICs. The 74HC Family use silicon gate CMOS technology to achieve operating speeds similar to the LSTTL family but with the low power consumption of standard CMOS integrated circuits.

74HC Family

€ 25,80

€ 0,516 1 kpl (50 kpl/putki) (ilman ALV)

€ 32,38

€ 0,648 1 kpl (50 kpl/putki) (Sis ALV:n)

50

€ 25,80

€ 0,516 1 kpl (50 kpl/putki) (ilman ALV)

€ 32,38

€ 0,648 1 kpl (50 kpl/putki) (Sis ALV:n)

Varastotiedot eivät ole tilapäisesti saatavilla.

50

Varastotiedot eivät ole tilapäisesti saatavilla.

Tekninen dokumentti

Tekniset tiedot

Merkki

NexperiaLogic Family

HC

Logic Function

D Type

Input Type

Single Ended

Output Signal Type

Differential

Triggering Type

Positive Edge

Polarity

Inverting, Non-Inverting

Mounting Type

Surface Mount

Package Type

SOIC

Pin Count

16

Set/Reset

Master Reset

Number of Elements per Chip

4

Maximum Propagation Delay Time @ Maximum CL

175 ns @ 2 V

Maximum Operating Supply Voltage

6 V

Dimensions

10 x 4 x 1.45mm

Height

1.45mm

Width

4mm

Minimum Operating Temperature

-40 °C

Minimum Operating Supply Voltage

2 V

Maximum Operating Temperature

+125 °C

Propagation Delay Test Condition

50pF

Length

10mm

Alkuperämaa

Thailand

Tuotetiedot

74HC Family Flip-Flops & Latches, Nexperia

A range of NXP Flip-Flops and Latches from the 74HC Family of CMOS Logic ICs. The 74HC Family use silicon gate CMOS technology to achieve operating speeds similar to the LSTTL family but with the low power consumption of standard CMOS integrated circuits.